**TRASMA**

**TINA**

**MUSE**

**FPGA-simple**

**CMS-I level**

**CMS-II level**

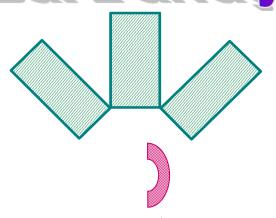

# BaF2 array

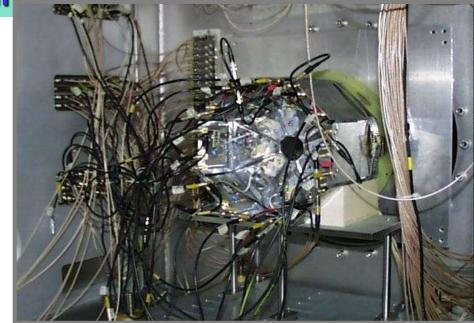

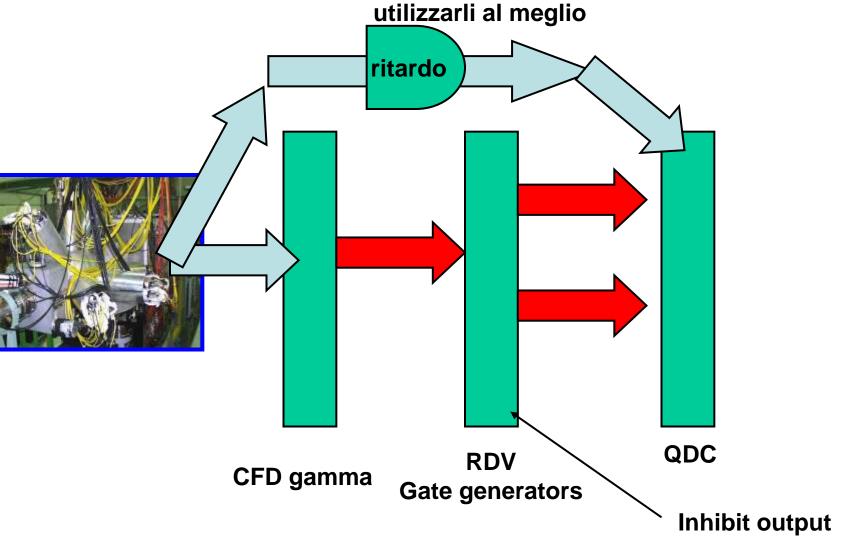

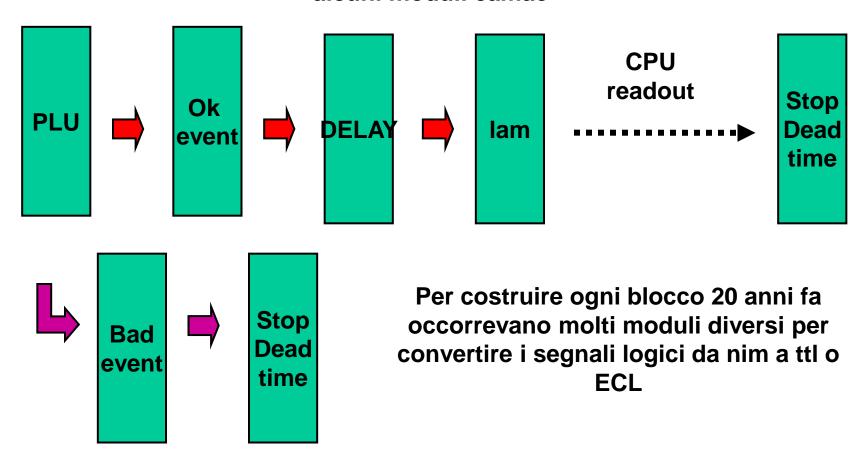

II trigger di TRASMA → trigger basato su moduli standard + PLU

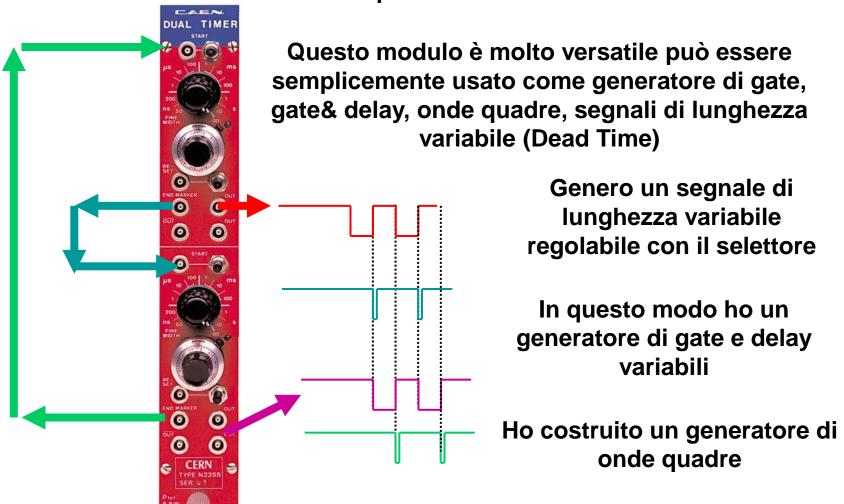

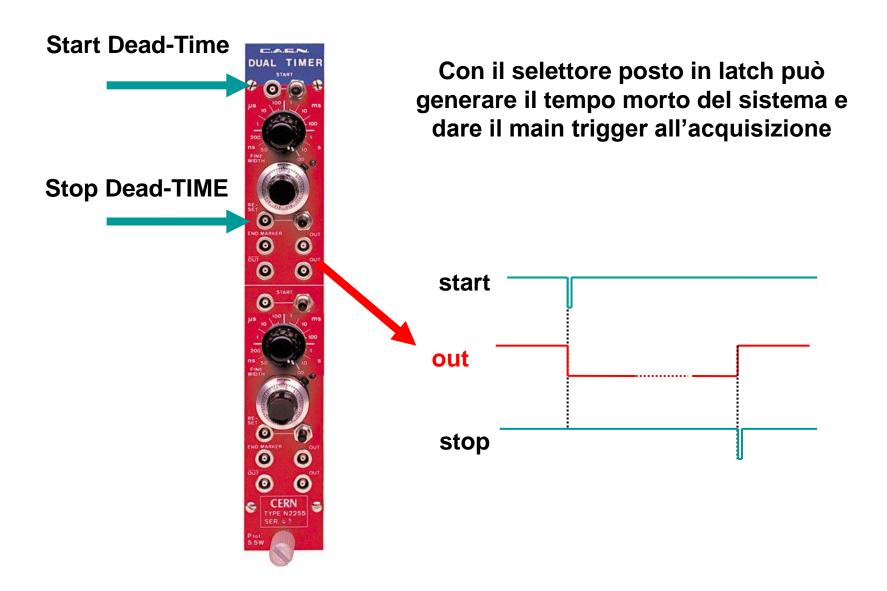

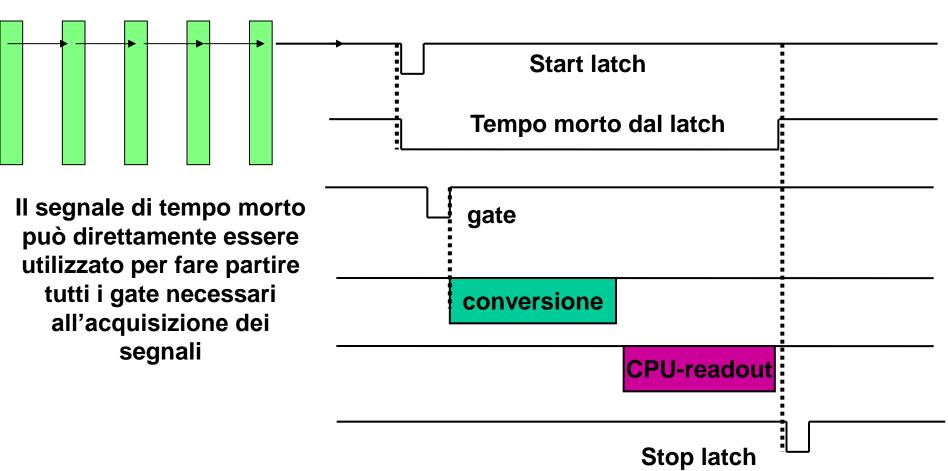

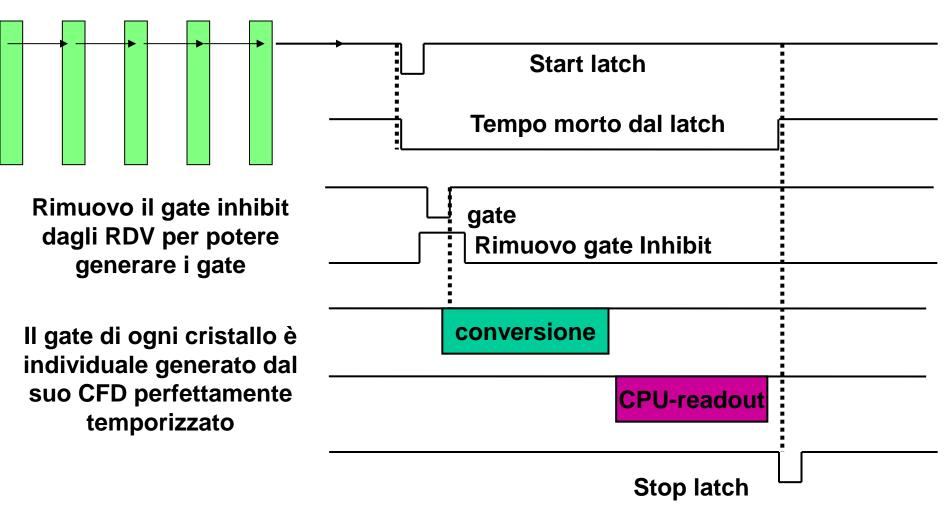

Il modulo centrale del trigger era un dual gate generator usato per la gestione del tempo morto

I discriminatori generano un segnale di molteplicità

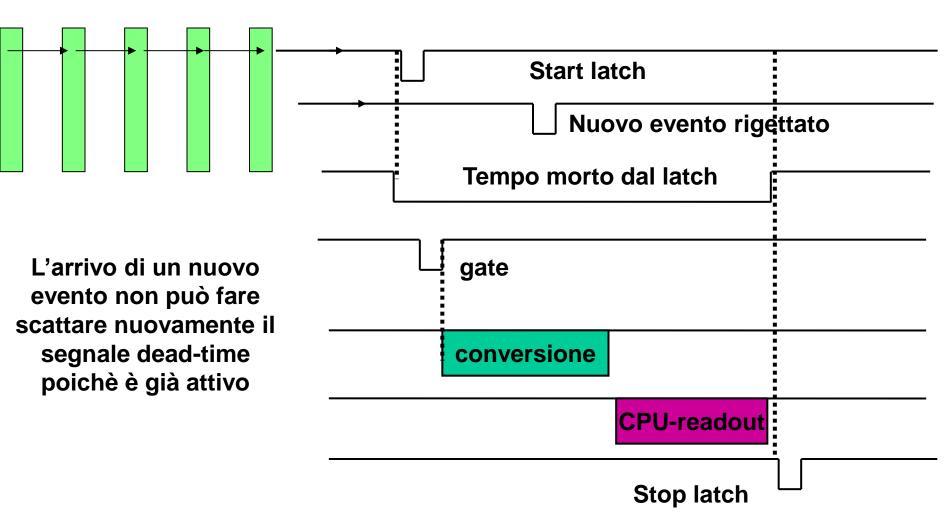

Il latch veta automaticamente la generazione di nuovi gate dovuti all'arrivo di altri segnali dai discriminatori

#### PARTICOLARITA' sistemi di trigger: TRASMA

Alcune particolarità di TRASMA che vi racconto non per usarle ma per spingervi a guardare bene tutte le caratteristiche dei moduli che avete a disposizione per

I discriminatori generano un segnale di molteplicità

TINA è stato il primo trigger integrato costruito dal reparto acq ed elettronica dei LNS

È basato su di un pattern unit da 16 bit

All'inizializzazione dobbiamo dichiarare le configurazioni di ingresso valide

All'arrivo di un evento la configurazione di ingresso viene analizzata e, se buona, si generano dei segnali che possono essere utilizzati per generare i gate

Può generare un clear nel caso di evento rigettato

Gestisce il segnale di tempo morto che parte

automaticamente e viene rimosso da un comando camac

che viene generato dalla CPU di readout

Gestisce il LAM (look at me) comunicando alla CPU che ci sono dati pronti da leggere negli ADC

Ha permesso di sostituire un trigger fatto da alcuni crate nim ed alcuni moduli camac

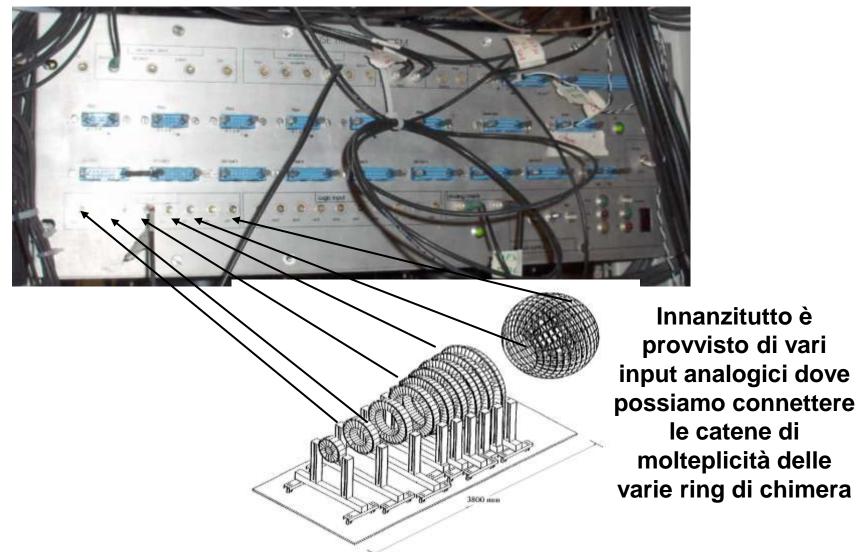

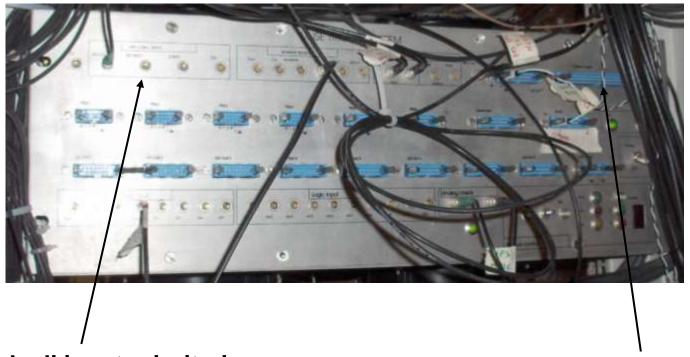

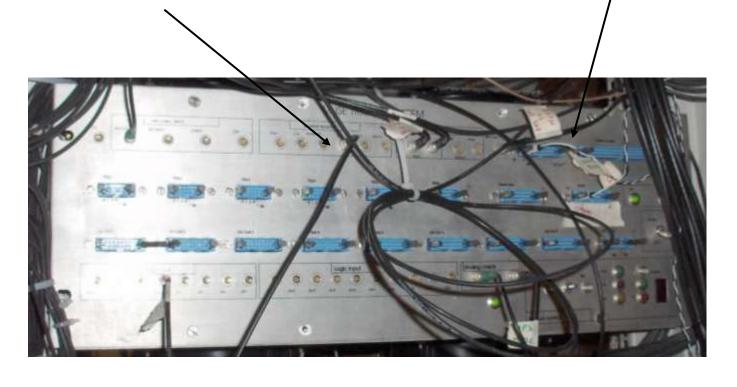

MUSE è un TINA enhanced in cui si è tentato di integrare sistemi logici e sistemi analogici lasciando molti margini di flessibilità per prevedere possibili accoppiamenti con diversi rivelatori

MUSE è un TINA enhanced in cui si è tentato di integrare sistemi logici e sistemi analogici lasciando molti margini di flessibilità per prevedere possibili accoppiamenti con diversi rivelatori

Se devo accoppiare un rivelatore esterno posso usare uno dei 10 input logici ulteriori

Ho un uscita or ed un uscita multiplexata da cui posso visualizzare le molteplicità in input

Ha degli input prioritari per un trigger di livello 0 cui solitamente colleghiamo il segnale di or che utilizziamo come master per ripulire le memorie di ingresso

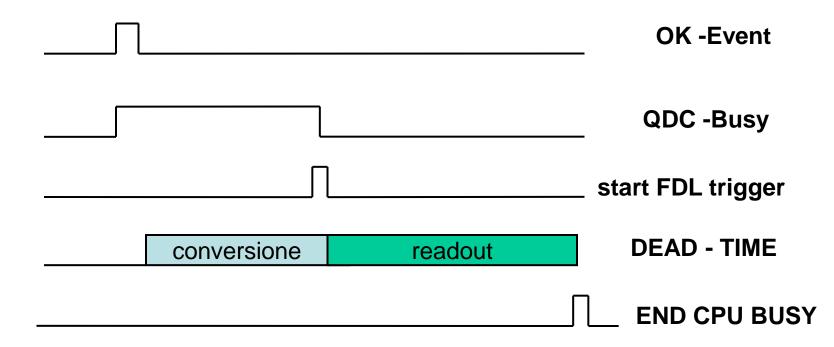

Ha input per il busy dei qdc per poterne meglio gestire il tempo morto

Ha ovviamente tanti output che ci servono per controllarne il funzionamento, tra cui le coincidence window ( tempo di attesa delle molteplicità e dei segnali logici) il tempo morto ..

l'output principale è il segnale di evento accettato, ma anche quello di evento rigettato per la generazione di eventuali clear

Per

temporizzare

bene i gate

aveva pure un

ingresso per la

radiofrequenza

del CS

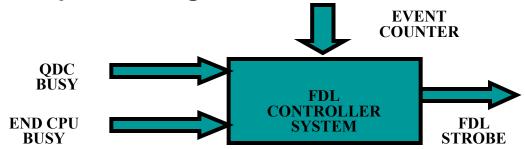

Era specializzato per la gestione di un sistema di readout basato su moduli FDL che avevano bisogno di un segnale TTL e di un pattern logico per fare partire il readout dei QDC Come tutti i moduli qualche lucetta accesa ti rassicura del fatto che ci sia la corrente

Avrebbe dovuto poter generare tutti i gate necessari per l'acquisizione ma questo non è stato poi realizzato per varie difficoltà realizzative

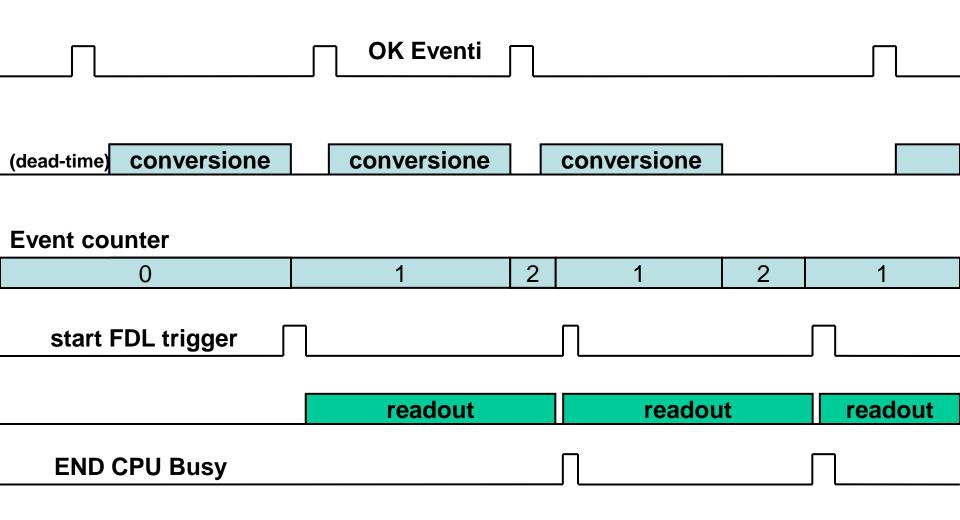

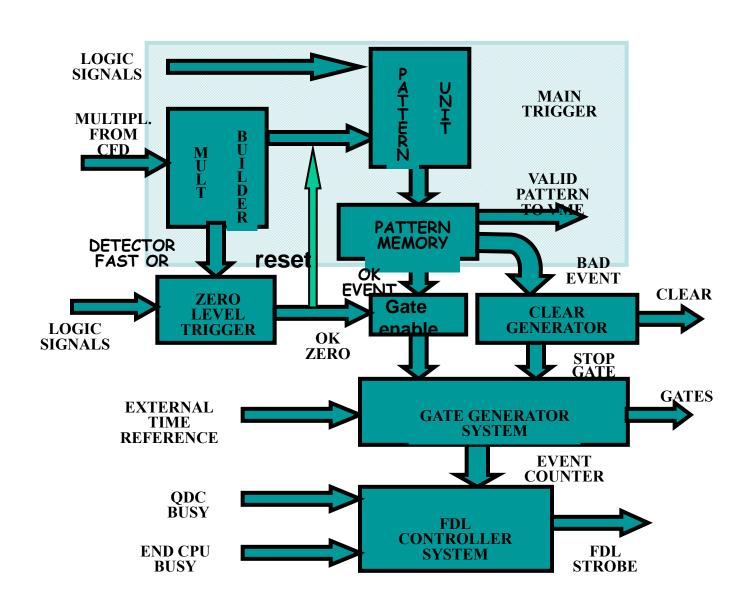

#### Vi racconto meglio la logica del trigger

Vediamo più in dettaglio il sistema di controllo del readout

Single event readout

Multi - event readout